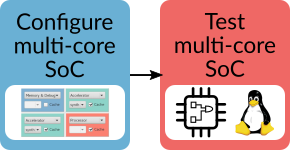

How to: design a multi-core SoC

Tutorial guide:

Tutorial video:

Note: The video tutorial was not recorded with the latest version of the ESP repository. While watching the video, please refer to the written tutorial guide for the most up to date instructions.

What you will learn

- Generate a multi-core ESP SoC with the ESP GUI and test it on FPGA

What you will need

- Prerequisites

- Equipment

- One of the supported FPGA boards (see homepage)

- (optional) An internet router

- (optional) Prebuilt material

- The FPGA bistream (

top.bit) generated in the tutorial - The Linux image (

linux.bin) generated in the tutorial - The baremetal binaries (

systest.bin,prom.bin) generated in the tutorial

- The FPGA bistream (

What you can read

NoC-Based Support of Heterogeneous Cache-Coherence Models for

Accelerators

Davide Giri, Paolo Mantovani, and Luca P. Carloni

In Proceedings of the IEEE/ACM International Symposium on Networks-on-Chip (NOCS), 2018

What you can contribute

The ESP team welcomes external contributions and collaborations on a variety of topics including but not limited to:

-

ESP multi-core with the Ariane processor

-

Bare-metal multi-core test suite for the Ariane processor

Check out our contributing guidelines.