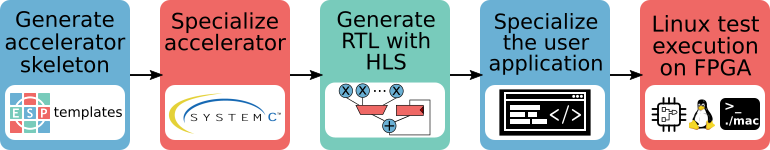

How to: design an accelerator in SystemC (Cadence Stratus HLS)

Tutorial guide:

Tutorial videos:

-

Part 1

-

Part 2

Note: The video tutorials were not recorded with the latest version of the ESP repository. While watching the videos, please refer to the written tutorial guide for the most up to date instructions.

What you will learn

- Generate a customized accelerator

- source code skeleton

- testbench

- Stratus HLS synthesis scripts

- device driver

- user-space application skeleton

- Implement accelerator-specific code

- computation kernel

- input and golden output

- validation

- Edit the HLS synthesis script

- Integrate a new accelerator into an ESP instance and test it on FGPA

What you will need

- Prerequisites

- Equipment

- One of the supported FPGA boards (see homepage)

- (optional) An internet router

- (optional) Prebuilt material

- The source code, testbench and Stratus HLS scripts for the MAC accelerator

- The device drivers for the MAC accelerator

- Two working folders for Xilinx VCU118 and Xilinx VC707

What you can read

High-Level Synthesis of Accelerators in Embedded Scalable

Platforms

Paolo Mantovani, Giuseppe Di Guglielmo and Luca P. Carloni

In Proceedings of the Asia and South Pacific Design Automation Conference (ASPDAC), 2016

What you can contribute

The ESP team welcomes external contributions and collaborations on a variety of topics including but not limited to:

-

Accelerator designs for a wide range of application domains

-

Support for more HLS tools

-

Support for accelerator design flows from domain-specific languages (DSL).

-

Power estimation flow

Check out our contributing guidelines.